# NDSPEED BUILD IT FIRST

# CX20501

Quad Multi-Rate CDR (65 Mbps - 3.2 Gbps) Data Sheet

## Contents

| Contents                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------|

| Applications                                                                                                              |

| Ordering Information                                                                                                      |

| Revision History                                                                                                          |

| Figure 1. Block Diagram                                                                                                   |

| Table 1. Terminal Functional Description    6                                                                             |

| Table 2. Power DC Electrical Specifications (1).    7                                                                     |

| Table 3. +3.3V CMOS DC Electrical Specifications (1,2)    8                                                               |

| Table 4. +2.5V CMOS DC Electrical Specifications <sup>(1)</sup> 8                                                         |

| Table 5. +3.3V PCML DC Electrical Specifications <sup>(1)</sup> 9                                                         |

| Table 6. +2.5V PCML DC Electrical Specifications <sup>(1)</sup> 9                                                         |

| Table 7. Recommended Operating Conditions    10                                                                           |

| Table 8. Absolute Maximum Ratings <sup>(1)</sup>                                                                          |

| Table 9. High-speed PCML or AC-Coupled RF Electrical Specifications <sup>(1)</sup> 11                                     |

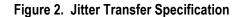

| Figure 2. Jitter Transfer Specification    12                                                                             |

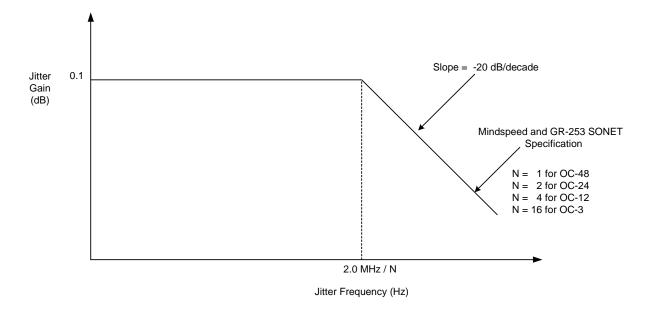

| Figure 3. Jitter Tolerance Specification (SONET specification: 0.15 UIpp at 1 MHz)                                        |

| Overview                                                                                                                  |

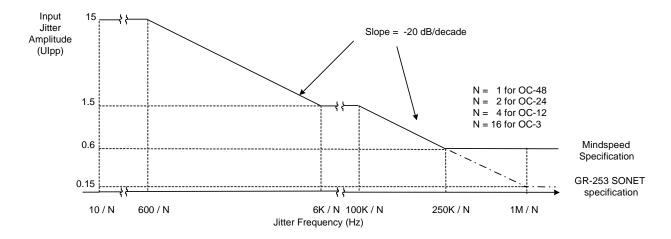

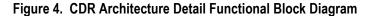

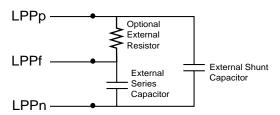

| Figure 4. CDR Architecture Detail Functional Block Diagram    13                                                          |

| Reserved and Common Addresses                                                                                             |

| CDR Architecture                                                                                                          |

| IC Partition                                                                                                              |

| Input Sensitivity/Input Duty Cycle                                                                                        |

| VCO Frequency Range                                                                                                       |

| Table 10. VCO Center Frequency Selection    15                                                                            |

| Table 11. Bit Rates of Potential Applications    15                                                                       |

| Table 12. 2.0 to 3.2 GHz Tuning Range Specification for AV <sub>DD</sub> = 3.3 V (VCO Center Frequency is Approximate) 15 |

| Table 13. 2.0 to 3.2 GHz Tuning Range Specification for AV <sub>DD</sub> = 2.5 V (VCO Center Frequency is Approximate) 15 |

| Frequency Acquisition                                                                                                     |

| Window Frequency Computation                                                                                              |

| Table 14. Example Register Settings for Wide and Narrow Frequency Windows (values are in decimal format) . | . 16 |

|------------------------------------------------------------------------------------------------------------|------|

| Data Phase Lock                                                                                            | . 17 |

| Loop Filter                                                                                                | . 17 |

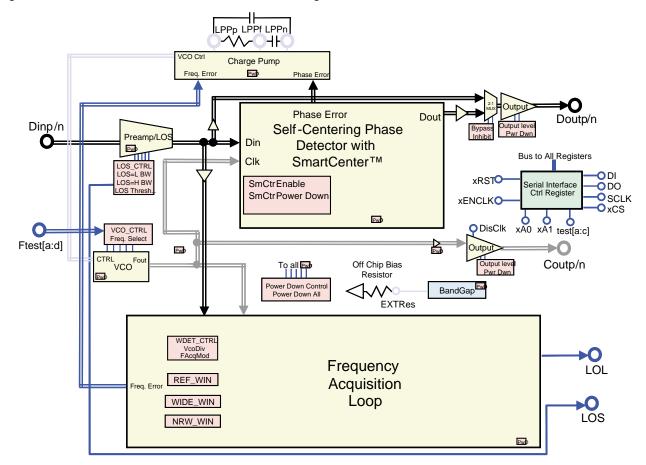

| Figure 5. Internal RC Loop Filter Fine Tune with Recommended External Capacitors                           | . 18 |

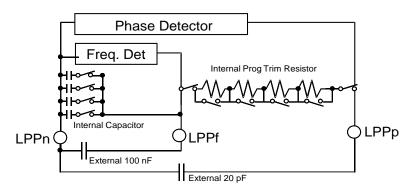

| Figure 6. External Loop Filter Configuration                                                               | . 18 |

| Table 15. Loop Filter Selection                                                                            | . 18 |

| Loss-Of-Signal                                                                                             | . 19 |

| Loss-Of-Signal and Loss-Of-Lock Bussing                                                                    | . 19 |

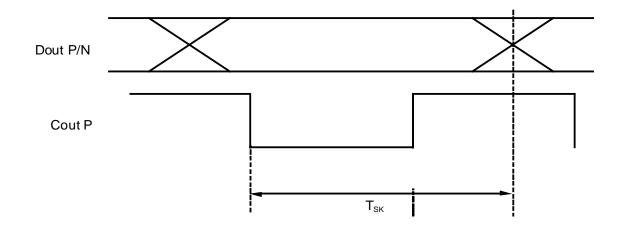

| Clock to Data Output Timing                                                                                | . 20 |

| Figure 7. Clock and Data Output Skew Timing                                                                | . 20 |

| Table 16. Clock to Data Output Skew                                                                        | . 20 |

| Table 17. Clock and Data Output Duty Cycle                                                                 | . 20 |

| CDR Bypass                                                                                                 | . 20 |

| Resetting the CDR                                                                                          | . 20 |

| Output Drive Level                                                                                         | . 21 |

| Other Features                                                                                             | . 21 |

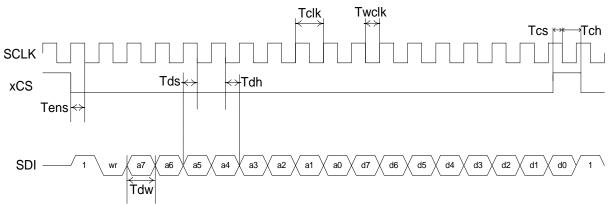

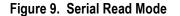

| Serial I/O Overview                                                                                        | . 21 |

| Timing Diagram: Clock Set and Program Modes                                                                | . 22 |

| Figure 8. Serial Write Mode                                                                                | . 22 |

| Figure 9. Serial Read Mode                                                                                 | . 22 |

| Table 18. Serial Interface Timing—Specified at Recommended Operating Conditions                            | . 23 |

| Table 19. Register Summary                                                                                 | . 24 |

| Table 20. Register Description                                                                             | . 25 |

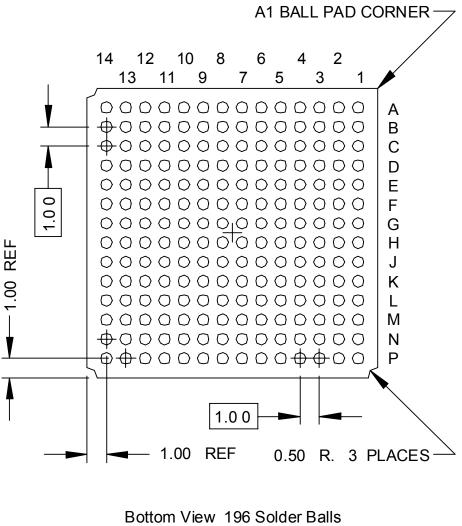

| Figure 10. BGA Package Ball Assignment Bottom View (assume package is transparent)                         | . 32 |

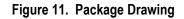

| Figure 11. Package Drawing                                                                                 | . 33 |

| Table 21. Ball Assignment Sorted by Ball Location.                                                         | . 34 |

| Table 22. Ball Assignment Sorted by Signal Name.                                                           | . 35 |

### **Key Features**

- Four independent CDRs, each running between 65 Mbps and 3.2 Gbps

- Jitter generation 7 mUI, Jitter Tolerance 0.6 UI typical

- Typical Total Power Consumption as low as 900 mW with all channels running

- · Per channel bypass mode for unsupported data rates

- Per channel power-down mode for unused channels

### Applications

- SONET OC-1, OC-3, OC-12, OC-48 systems and modules

- InfiniBand systems and modules

- Digital Video Applications (SDI and HDI)

- Fibre Channel (1x, 2x, 10x) systems

- Gigabit Ethernet systems

- 10GBASE-LX4 XAUI systems & modules

- ESCON, FDDI, NTSC/PAL systems and modules

- Backplane reach extension

### **Product Description**

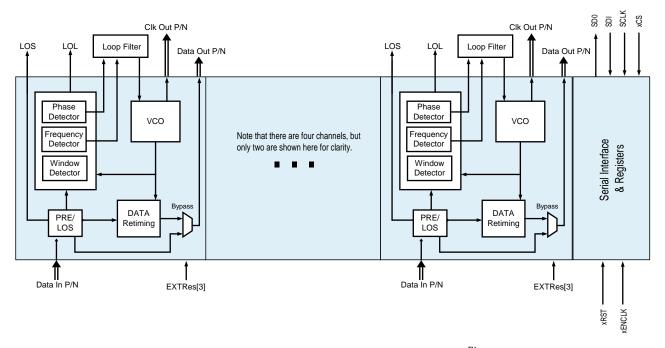

The CX20501 is a quad Clock and Data Recovery (CDR) circuit designed for +3.3 or +2.5 V low power operation. As a multi-rate device, it can support data rates from 65 Mbps to 3.2 Gbps. Because each CDR operates independently, each can lock to a common frequency or to a separate frequency to support diverse applications without an external frequency reference. A quasi-limiting amplifier is used to improve the input sensitivity of the device. To save power, the individual output clocks and/or CDRs can be powered down and the output drive level is also selectable. The high-speed I/O is differential Positive Current Mode Logic (PCML) with an on-chip 50  $\Omega$  to Vdd (single-ended) input termination/output backmatch. The I/O can be used either differentially or single-ended. A serial interface (+3.3 V/+2.5 V CMOS) is used to fine-tune the frequency acquisition characteristics and the operating bit-rate. Alarms are provided for both Loss Of Lock (LOL) and Loss Of Signal (LOS), and a CDR bypass feature allows direct connection of the input data to the output buffer without re-timing. The CX20501 I/O pin configuration is a drop-in replacement for the OC-48 CX20464 single-rate quad CDR and complements all of Mindspeed's crosspoint switches. Figure 1 illustrates the quad CDR IC functional block diagram and Table 1 through Table 9 list the CX20501 electrical specifications.

#### **Ordering Information**

| Name Number |                             | Number     | Package Data        |

|-------------|-----------------------------|------------|---------------------|

|             | CX20501 Quad Multi-rate CDR | CX20501-12 | 15 mm BGA (196 pin) |

#### **Revision History**

| Revision | Date  | Comments                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. C   | 4/02  | Converted document to new format.<br>Expanded introduction section.<br>Loop Filter description rewritten.<br>LOS description rewritten.<br>Figures 6 and 7 were added.<br>Tables 1, 2, 3, 4, 6, 7, 8, 9, 10, 17, 18, and 19 were updated.                                                                                                                                                        |

| Rev. D   | 6/02  | Figure 1 redrawn. Figures 4, 5, 10 and 11 updated. Table 14 added. Tables 1, 3, 4, 5, 6, 7, 9, 10, 12, 13, 20 (Output Buffer Level and VCO Control), 21 and 22 updated.                                                                                                                                                                                                                          |

| Rev. E   | 9/02  | Tables 8, 9, 10, 11, 13, 14, 20, and 21 were updated. Inserted new Table 18. Revised Figures 7 and 9. Revised the following sections: CDR Archecture, Input Sensitivity/Input Duty Cycle, VCO Frequency Range, Window Frequency Computation, Loop Filter, Loss-Of-Signal and Loss-Of-Lock Bussing, CDR Bypass, Output Drive Level, Other Features, Timing Diagrams: Clock Set and Program Modes. |

| Rev. A   | 12/02 | Revised Document Number.                                                                                                                                                                                                                                                                                                                                                                         |

| Rev. B   | 3/03  | Updated specifications with electrical characterization results.                                                                                                                                                                                                                                                                                                                                 |

#### Figure 1. Block Diagram

SmartCenter<sup>TM</sup> patent no. US 6,316,966 B1 granted Nov 13, 2001

### Introduction

This document uses the following text styling conventions: CDR signal names and terminal numbers are listed with initial caps denoting each functional name part, with its related signal polarity indicated by an upper case 'N' or 'P'. Thus, data input signal names are indicated, for example as: 'DinP' and 'DinN'.

A signal name and an associated CDR channel number (0 through 3) are indicated as DinP[n] and DinN[n] where 'n' is a channel number. Register names are preceded by the word 'register' and typed in all upper case with each functional name part separated by an underscore. Additionally, brackets group register bit numbers, and sub-function parts are in initial caps such as for example: 'register CONTROL\_FUNCTION[5:4] Los\_hyst'.

**Note**: There is no space between the name and the first bracket, and a space after the last bracket. The underscore is unique to hysteresis related register names and not universally used in the CX20501 functional description.

Because this unit has four identical CDRs, unless otherwise noted, the same register name applies to each CDR but different addresses describe an unique register.

To better distinguish terminal names from internal signal names the word terminal is included in all references to input, output, or control terminals, such as for example only: 'terminal LOS controls that function', and 'when the LOS terminal = H this function occurs'. In a similar manner references to signal names include the word signal.

### Table 1. Terminal Functional Description

| Name                    | Function                                                               | Notes | Туре | Signal        |

|-------------------------|------------------------------------------------------------------------|-------|------|---------------|

| DinP[3:0]               | Positive high-speed data input                                         | 1     | I    | PCML          |

| DinN[3:0]               | Negative high-speed data input                                         | 1     | I    | PCML          |

| DoutP[3:0]              | Positive high-speed data output                                        | _     | 0    | PCML          |

| DoutN[3:0]              | Negative high-speed data output                                        | _     | 0    | PCML          |

| CoutP[3:0]              | Positive recovered clock output                                        | _     | 0    | PCML          |

| CoutN[3:0]              | Negative recovered clock output                                        | _     | 0    | PCML          |

| LOS[3:0]                | Loss of signal                                                         | 5     | 0    | CMOS          |

| LOL[3:0]                | Loss of lock                                                           | 5     | 0    | CMOS          |

| LPPp[3:0]               | Positive external loop filter (phase detector)                         | —     | А    | Analog        |

| LPPn[3:0]               | Negative external loop filter (phase detector)                         | —     | А    | Analog        |

| LPPf[3:0]               | Positive external loop filter (frequency detector)                     | 2     | А    | Analog        |

| EXTres[3:0]             | External reference resistor (12 K $\Omega$ +/- 1% to V <sub>SS</sub> ) | _     | А    | Analog        |

| SClk                    | Serial I/O clock                                                       | -     | I    | CMOS          |

| xCS                     | Chip select: active low I/O enable                                     | -     | I    | CMOS          |

| SDI                     | Serial data input                                                      | -     | I    | CMOS          |

| SDO                     | Serial data output (high - Z state when not selected)                  | —     | 0    | CMOS          |

| xENClk                  | Global HS output clock enable (active low)                             | —     | I    | CMOS          |

| xRST                    | Reset to default state (active Low)                                    | —     | I    | CMOS          |

| AV <sub>DD</sub> C      | Positive supply for CDR core                                           | 3     | Р    | PWR           |

| AV <sub>DD</sub> O      | Positive supply for output drivers                                     | 3     | Р    | PWR           |

| AV <sub>DD</sub> V[3:0] | Positive supply for VCO                                                | 3     | Р    | PWR           |

| AV <sub>SS</sub> C      | Negative supply for CDR core                                           | 3     | Р    | PWR           |

| AV <sub>SS</sub> O      | Negative supply for output driver                                      | 3     | Р    | PWR           |

| AV <sub>SS</sub> V[3:0] | Negative supply for VCO                                                | 3     | P    | PWR           |

| DV <sub>DD</sub>        | Positive digital supply                                                | 3     | P    | PWR           |

| DV <sub>SS</sub>        | Negative digital supply                                                | 3     | Р    | PWR           |

| Ftest[3:0,d:a]          | Mindspeed Technologies test pins                                       | 4     | I    | MSPD reserved |

| Test[3:0,c:a]           | Mindspeed Technologies test pins                                       | 4     | I/O  | MSPD reserved |

#### Table 1. Terminal Functional Description

| Name                    | Function                                                        | Notes          | Туре            | Signal                      |

|-------------------------|-----------------------------------------------------------------|----------------|-----------------|-----------------------------|

| Notes:                  |                                                                 |                |                 | •                           |

| 1. Higher input sensiti | vity and common-mode range over standard PCML.                  |                |                 |                             |

| 2. LPPf is a separate   | pin for lower noise.                                            |                |                 |                             |

|                         | ower and grounds are maintained for all four CDRs and connected | ed together wi | ith a low induc | ctance plane in the package |

| 4. Leave Mindspeed t    | est pins floating.                                              |                |                 |                             |

| 5. Various signals from | n different CDRs can be connected in parallel to form a LOS/LOI | bus if enable  | ed in the OUT   | RF_CTRI [5:4] register      |

### Table 2. Power DC Electrical Specifications <sup>(1)</sup>

| Symbol                 | Item                                       | Notes | Minimum | Typical | Maximum | Units |

|------------------------|--------------------------------------------|-------|---------|---------|---------|-------|

| Diss                   | DV <sub>DD</sub> : control logic           | 2     | _       | 0.23    | .75     | mA    |

| AissC                  | AV <sub>DD</sub> C: CDR core/per CDR       | _     | _       | 46      | 48      | mA    |

| AissV                  | AV <sub>DD</sub> V: VCO/per CDR            | 2     | _       | 20      | 21      | mA    |

| AissO                  | AV <sub>DD</sub> O: output drivers/per CDR | 2, 3  | _       | 24      | 25      | mA    |

| I <sub>total</sub>     | Total current/per CDR                      | 2     | _       | 90      | 93      | mA    |

| P <sub>diss</sub> /CDR | Total power dissipation per CDR            | 4     | -       | 300     | 330     | mW    |

| P <sub>diss</sub>      | Total quad power dissipation               | 4, 5  | -       | 1.2     | 1.32    | W     |

Notes:

1. Specified at Recommended Operating Conditions. See Table 7.

2. Total current computed per CDR channel

3. Computed with clock outputs disabled, data outputs in low output swing mode, and phase lock loop (PLL) in lock

4. Typical  $\mathsf{P}_{diss}$  computed at +3.3 V and maximum PDISS computed at +3.6 V

5. With both clock and data outputs enabled on all four CDRs in high-swing mode, typically, power dissipation is 1.6W

| Symbol          | Item                                      | Notes | Minimum               | Typical | Maximum               | Units |

|-----------------|-------------------------------------------|-------|-----------------------|---------|-----------------------|-------|

| V <sub>OH</sub> | Output logic high $I_{OH}$ = -100 µA      | -     | 3.0                   | 3.2     | —                     | V     |

| V <sub>OH</sub> | Output logic high I <sub>OH</sub> = -3 mA | -     | 2.8                   | 3.0     | —                     | V     |

| V <sub>OL</sub> | Output logic low $I_{OL}$ = 100 $\mu$ A   | -     | —                     | 0.08    | 0.4                   | V     |

| V <sub>OL</sub> | Output logic low I <sub>OL</sub> = 3 mA   | -     | —                     | 0.24    | 0.65                  | V     |

| V <sub>OL</sub> | Output logic low I <sub>OL</sub> = 16 mA  | -     | —                     | 0.64    | 0.85                  | V     |

| I <sub>OH</sub> | Output current (logic high)               | -     | -3.0                  | —       | 0                     | mA    |

| I <sub>OL</sub> | Output current (logic low)                | -     | 0                     | —       | 3.0                   | mA    |

| V <sub>IH</sub> | Input logic high                          | -     | 1.5                   | —       | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub> | Input logic low                           | -     | V <sub>SS</sub> – 0.3 | —       | 1.4                   | V     |

| I <sub>IH</sub> | Input current (logic high)                | -     | -380                  | —       | 460                   | nA    |

| IIL             | Input current (logic low)                 | -     | -13                   | —       | 0                     | μA    |

Table 3. +3.3V CMOS DC Electrical Specifications <sup>(1,2)</sup>

Table 4. +2.5V CMOS DC Electrical Specifications<sup>(1)</sup>

| Symbol          | Item                                       | Notes | Minimum               | Typical | Maximum               | Units |

|-----------------|--------------------------------------------|-------|-----------------------|---------|-----------------------|-------|

| V <sub>OH</sub> | Output logic high $I_{OH}$ = -100 µA       | -     | 1.5                   | 2.13    | -                     | V     |

| V <sub>OH</sub> | Output logic high $I_{OH} = -3 \text{ mA}$ | —     | 1.35                  | 1.95    | _                     | V     |

| V <sub>OL</sub> | Output logic low $I_{OL}$ = 100 $\mu$ A    | -     | —                     | 0.4     | 1.4                   | V     |

| V <sub>OL</sub> | Output logic low I <sub>OL</sub> = 3 mA    | _     | _                     | 0.54    | 1.25                  | V     |

| V <sub>OL</sub> | Output logic low I <sub>OL</sub> = 16 mA   | _     | _                     | 0.78    | 1.12                  | V     |

| I <sub>OH</sub> | Output current (logic high)                | _     | -3.0                  | _       | 0                     | mA    |

| I <sub>OL</sub> | Output current (logic low)                 | -     | 0                     | —       | 3.0                   | mA    |

| V <sub>IH</sub> | Input logic high                           | -     | 1.1                   |         | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub> | Input logic low                            | -     | V <sub>SS</sub> – 0.3 |         | 1.0                   | V     |

| IIH             | Input current (logic high)                 | -     | -380                  |         | 460                   | nA    |

| IIL             | Input current (logic low)                  | _     | -13                   | _       | 0                     | μA    |

1. Specified at Recommended Operating Conditions. See Table 7.

### Table 5. +3.3V PCML DC Electrical Specifications<sup>(1)</sup>

| Parameter                                             | Notes | Minimum               | Typical | Maximum               | Units |

|-------------------------------------------------------|-------|-----------------------|---------|-----------------------|-------|

| Input differential voltage (peak-to-peak)             | 2, 4  | 20                    | _       | 1200                  | mV    |

| Input common-mode voltage                             | 3, 4  | V <sub>DD</sub> - 500 | _       | V <sub>DD</sub> + 100 | mV    |

| Differential output voltage—high swing (peak-to-peak) | 2     | 730                   | _       | 960                   | mV    |

| Differential output voltage—low swing (peak-to-peak)  | 2     | 410                   | _       | 560                   | mV    |

| Low swing: output logic high                          | 5     | V <sub>DD</sub> - 40  | _       | V <sub>DD</sub>       | mV    |

| Low swing: output logic low                           | 5     | V <sub>DD</sub> - 280 | _       | V <sub>DD</sub> - 240 | mV    |

| High swing: output logic high                         | 5     | V <sub>DD</sub> - 45  | _       | V <sub>DD</sub>       | mV    |

| High swing: output logic low                          | 5     | V <sub>DD</sub> - 480 | —       | V <sub>DD</sub> - 400 | mV    |

Notes:

1. Specified at Recommended Operating Conditions. See Table 7.

2. Example 1200 mV differential peak-to-peak translates to 600 mV peak-to-peak for each single-ended terminal

3. Designed for DC-coupled PCML or AC-coupled CML, PECL, ECL (ECL may require off-chip attenuation)

4. Absolute maximum differential input voltage and common mode not to exceed V<sub>DD</sub> +300 mV

5. Output high and output low values are RMS measured values.

6. Clock output swing is typically 60% of data output swing.

### Table 6. +2.5V PCML DC Electrical Specifications <sup>(1)</sup>

| Parameter                                             | Notes | Minimum               | Typical | Maximum               | Units |

|-------------------------------------------------------|-------|-----------------------|---------|-----------------------|-------|

| Input differential voltage (peak-to-peak)             | 2, 4  | 20                    | _       | 1200                  | mV    |

| Input common-mode voltage                             | 3, 4  | V <sub>DD</sub> - 500 | _       | V <sub>DD</sub> + 100 | mV    |

| Differential output voltage—high swing (peak-to-peak) | 2     | 720                   | _       | 900                   | mV    |

| Differential output voltage—low swing (peak-to-peak)  | 2     | 380                   | _       | 520                   | mV    |

| Low swing: output logic high                          | 5     | V <sub>DD</sub> - 40  | _       | V <sub>DD</sub>       | mV    |

| Low swing: output logic low                           | 5     | V <sub>DD</sub> - 260 | _       | V <sub>DD</sub> - 225 | mV    |

| High swing: output logic high                         | 5     | V <sub>DD</sub> – 45  | _       | V <sub>DD</sub>       | mV    |

| High swing: output logic low                          | 5     | $V_{DD} - 450$        |         | V <sub>DD</sub> - 380 | mV    |

Notes:

1. Specified at Recommended Operating Conditions. See Table 7.

2. Example 1200 mV differential peak-to-peak translates to 600 mV peak-to-peak for each single-ended terminal.

3. Designed for DC-coupled PCML or AC-coupled CML, PECL, ECL (ECL may require off-chip attenuation).

4. Absolute maximum differential input voltage and common mode not to exceed V<sub>DD</sub> + 300 mV.

5. Output high and output low values are RMS measured values.

6. Clock output swing is typically 80% of data output swing.

### Table 7. Recommended Operating Conditions

| Parameter                                                                                                                          | Notes | Symbol          | Minimum | Typical | Maximum | Units |

|------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|---------|---------|---------|-------|

| Core Supply Voltage                                                                                                                | 1     | AvddC           | _       | 2.5/3.3 | _       | V     |

| Output Supply Voltage                                                                                                              | 1     | AvddO           | —       | 2.5/3.3 | -       | V     |

| Program Supply Voltage                                                                                                             | 1     | DVddP           | —       | 2.5/3.3 | —       | V     |

| VCO Supply Voltage                                                                                                                 | 1     | AvddV           | —       | 2.5/3.3 | —       | V     |

| Case Temperature                                                                                                                   | —     | Tc              | 0       | _       | +100    | °C    |

| Case to ambient thermal resistance                                                                                                 | 2     | θ <sub>ca</sub> | _       | 18      |         | °C/W  |

| Case to ambient thermal resistance                                                                                                 | 3     | $\theta_{ca}$   | —       | 23      | —       | °C/W  |

| Note:<br>1. Product will operate with +2.5 V $\pm$ 5% or +3.3 V $\pm$ 10%<br>2. $\theta_{ca}$ with an airflow velocity of 1 m/sec. | %     | 1               | 1       |         | 1       |       |

3.  $\theta_{\text{ca}}$  with no airflow, convection cooling only.

## Table 8. Absolute Maximum Ratings <sup>(1)</sup>

| Symbol                 | Item                   | Minimum | Maximum | Units |

|------------------------|------------------------|---------|---------|-------|

| DVddP                  | Program supply voltage | _       | 3.6     | V     |

| AVddC                  | Core supply voltage    | _       | 3.6     | V     |

| AVddO                  | Output supply voltage  | _       | 3.6     | V     |

| AVddV                  | VCO supply voltage     | _       | 3.6     | V     |

| Tst                    | Storage temperature    | -65     | +150    | °C    |

| ESD                    | Human body model       | 1500    | _       | V     |

| ESD                    | Charge device model    | 200     | _       | V     |

| Note:<br>1. No Damage. |                        | •       |         |       |

| Parameter                              | Notes       | Minimum | Typical | Maximum | Units  |

|----------------------------------------|-------------|---------|---------|---------|--------|

| Input Bit Rate (NRZ data)              | 2, 4, 7, 9  | 2.0/N   | —       | 3.2/N   | Gbps   |

| Jitter Transfer                        | 4, 9        | —       | —       | _       | Figure |

| Jitter Tolerance                       | 4, 9        | —       | _       | _       | Figure |

| Jitter Tolerance > 250 kHz             | 9           | 0.6     | —       | _       | UI p-p |

| Clock Jitter Generation (RMS)          | 3, 4, 6, 10 | —       | —       | 0.007   | UI rms |

| Clock Jitter Generation (peak-to-peak) | 3, 4, 6, 10 | —       | —       | 0.063   | UI p-p |

| Data Output Jitter (RMS)               | 6, 8, 9     | —       | 7       | 12      | ps     |

| Data Output Jitter (peak-to-peak)      | 6, 8, 9     | —       | 44      | 60      | ps     |

| Adjacent Channel Isolation             | 11          | 30      | —       | _       | dB     |

| Rise Time/ Fall Time (20 to 80%)       | 6, 11       | _       | —       | 100     | ps     |

| Output Return Loss (40 MHz to 2.5 GHz) | 5, 6, 11    | —       | -15.0   | _       | dB     |

| Output Return Loss (2.5 GHz to 5 GHz)  | 5, 6, 11    | —       | -5.0    | —       | dB     |

| Input Return Loss (40 MHz to 2.5 GHz)  | 5, 6, 9     | —       | -15.0   | _       | dB     |

| Input Return Loss (2.5 GHz to 5 GHz)   | 5, 6, 9     | —       | -5.0    | _       | dB     |

| Table 9. | High-speed PCML | . or AC-Coupled RF | Electrical S | pecifications <sup>(1)</sup> |

|----------|-----------------|--------------------|--------------|------------------------------|

|----------|-----------------|--------------------|--------------|------------------------------|

Notes:

1. Specified at Recommended Operating Conditions. See Table 7.

2. Default operation for OC-48 with VCO centered at 2.48832 GHz, device can be programmed to operate at data rates from 2.0/N to 3.2/N Gbps.

3. Measurement jitter bandwidth is 12 kHz to 20 MHz. Clock jitter generation measured per SONET standards.

4. Tested with 50 mV p-p differential input and 2<sup>23</sup>-1 PRBS pattern.

5. Return loss computed with worst case > 3 sigma 20% variation of resistance

6. Performance specifications listed are for data rates of 2.488 Gbps

7. N = 1, 2, 4, 8, 16, or 32

8. Peak-to-peak jitter increases by approximately 0.06 ps/Mbps at data rates above 2.488 Gbps. RMS jitter increases proportionally.

9. This specification only applies to data.

10. This specification only applies to clock output.

11. This specification applies to both clock and data output.

## MNDSPEED

## CX20501 Quad Multi-Rate CDR (65 Mbps - 3.2 Gbps)

Figure 3. Jitter Tolerance Specification (SONET specification: 0.15 Ulpp at 1 MHz)

### **Functional Description**

#### Overview

Figure 4 illustrates the detailed functional block diagram of individual CDRs (the serial interface is not repeated). A serial interface (described in the next section) provides access to the numerous features and options stored in the CX20501 internal memory register.

Table 19 contains a summary of register names, addresses, and bit functions. Table 20 contains a detailed description of the register functions.

#### **Reserved and Common Addresses**

The following addresses are reserved for various CDRs: 00h-0Dh for CDR#0 40h-4Dh for CDR#1 80h-8Dh for CDR#2 C0h-CDh for CDR#3 Addresses 20h to 25h are common to all four CDRs

#### **CDR Architecture**

A limiting preamplifier improves input sensitivity and amplifies input data (DinP/DinN) to remove input duty cycle offsets before extracting the recovered clock (CoutP/CoutN) and re-timing the data (DoutP/DoutN).

The input data also passes through a loss-of-signal (LOS) detector to determine if the input signal exceeds a threshold of approximately 240 mV. This design feature, which is based on a self-centering phase detector with a built-in decision circuit, prevents the CDR from locking to noise from a coupled channel. Patented SmartCenter<sup>™</sup> topology maintains a centered decision point regardless of data transition density changes (e.g. in the A1/A2 bytes of a SONET header).

SmartCenter<sup>™</sup> also keeps the clock centered in the phase margin of the decision flip-flop regardless of temperature, process, and power supply variations. This assures maximum jitter tolerance above the 100 KHz pole.

A frequency detector (FD) works with a frequency window detector (FWD) for frequency acquisition in the absence of an external timing reference. This allows each CDR to operate at different frequencies, which is not achievable with reference based CDRs.

For example, some CDRs can lock to 2.488 Gbps while others may lock at 2.6 or 3.2 Gbps data rates. If the VCO frequency is within the programmable window, the frequency acquisition loop is shut off, so the CDR PLL can achieve phase lock. If not, the frequency acquisition loop is enabled to aid acquisition. The frequency windows differ to increase robustness; the out-of-lock default is: 4,167 ppm and the in-lock default is 93,750 ppm.

#### IC Partition

All CDRs are identical and each uses a separate on-chip power supply and ground. The individual supplies are connected to low inductance planes within the package; however, each VCO supply is individually brought out for maximum isolation.

Both the positive and negative power supplies are expected to be planes on the printed circuit board (PCB) and all power pins should be bypassed according to standard practices.

The four pairs of supply voltages:  $AV_{DD}Vn/AV_{SS}Vn$  (n = 0, 1, 2, 3) should each be bypassed with a large electrolytic capacitor (4.7  $\mu$ F or larger) along with smaller high-speed capacitors. Unused I/Os and CDRs can be individually powered off to save power and reduce possible sources of crosstalk.

#### Input Sensitivity/Input Duty Cycle

For improved input sensitivity, input data passes through a preamplifier/quasi-limiting amplifier to amplify the attenuated data signal to full internal logic swing. The differential input sensitivity is 20 mV p-p, which translates to 10 mV p-p on each single-ended input for full logic level into the decision flip-flop. A duty cycle correction servo with a low 3 dB cutoff point of 8 kHz corrects for possible input duty cycle distortion. When enabled, the servo removes any input offset to attain a 50% duty cycle output to the internal decision circuit. To enable this feature, set PD\_CTRL0[7] = 0 (default is disabled).

#### VCO Frequency Range

The default VCO frequency is centered at 2.488 GHz for OC-48 operation. However, to support FEC and non-SONET applications, the VCO frequency can be moved with the VCO\_CTRL[6:4] registers. The frequency range is from 2.0 GHz to approximately 3.2 GHz. Mindspeed Technologies centers the OC-48 default setting; the other ranges are approximate. Table 10 and Table 11 show the center frequencies and applications. Table 12 and Table 13 specify the tuning range of each of the center frequencies, grouped by power supply.

| Divider Ratio | Ctrl5  | Ctrl4  | Ctrl3  | Ctrl2  | Ctrl1  | Ctrl0  | Unit |

|---------------|--------|--------|--------|--------|--------|--------|------|

| Divide by 1   | 3200.0 | 3000.0 | 2750.0 | 2500.0 | 2250.0 | 2000.0 | MHz  |

| Divide by 2   | 1600.0 | 1500.0 | 1375.0 | 1250.0 | 1125.0 | 1000.0 | MHz  |

| Divide by 4   | 800.0  | 750.0  | 687.5  | 625.0  | 562.5  | 500.0  | MHz  |

| Divide by 8   | 400.0  | 375.0  | 343.8  | 312.5  | 281.3  | 250.0  | MHz  |

| Divide by 16  | 200.0  | 187.5  | 171.9  | 156.3  | 140.6  | 125.0  | MHz  |

| Divide by 32  | 100.0  | 93.8   | 85.9   | 78.1   | 70.3   | 62.5   | MHz  |

### Table 10. VCO Center Frequency Selection

#### Table 11. Bit Rates of Potential Applications

| Divider Ratio | SONET<br>FEC2 | ESCON  | HDTV   | SONET<br>FEC | GigEtherNet | SONET  | D1 Video | FibChan | Sysplex | FDDI   | Fast Ether | Unit |

|---------------|---------------|--------|--------|--------------|-------------|--------|----------|---------|---------|--------|------------|------|

| Divide by 1   | 3200.0        | 3200.0 | 2970.0 | 2700.0       | 2500.0      | 2488.3 | 2160.0   | 2124.0  | 2048.0  | 2000.0 | 2000.0     | MHz  |

| Divide by 2   | 1600.0        | 1600.0 | 1485.0 | 1350.0       | 1250.0      | 1244.2 | 1080.0   | 1062.0  | 1024.0  | 1000.0 | 1000.0     | MHz  |

| Divide by 4   | 800.0         | 800.0  | 742.5  | 675.0        | 625.0       | 622.1  | 540.0    | 531.0   | 512.0   | 500.0  | 500.0      | MHz  |

| Divide by 8   | 400.0         | 400.0  | 371.3  | 337.5        | 312.5       | 311.0  | 270.0    | 266.0   | 256.0   | 250.0  | 250.0      | MHz  |

| Divide by 16  | 200.0         | 200.0  | 185.6  | 168.8        | 156.3       | 155.5  | 135.0    | 133.0   | 128.0   | 125.0  | 125.0      | MHz  |

| Divide by 32  | 100.0         | 100.0  | 92.8   | 84.4         | 78.1        | 77.8   | 67.5     | 66.5    | 64.0    | 62.5   | 62.5       | MHz  |

Table 12. 2.0 to 3.2 GHz Tuning Range Specification for AV<sub>DD</sub> = 3.3 V (VCO Center Frequency is Approximate)

| VCO Setting (GHz) | AV <sub>DD</sub> = 3.3 V |               |  |  |  |  |

|-------------------|--------------------------|---------------|--|--|--|--|

|                   | VCO Min (GHz)            | VCO Max (GHz) |  |  |  |  |

| 2.0               | 2.04                     | 2.20          |  |  |  |  |

| 2.25              | 2.22                     | 2.43          |  |  |  |  |

| 2.5               | 2.48                     | 2.71          |  |  |  |  |

| 2.75              | 2.65                     | 2.87          |  |  |  |  |

| 3.0               | 2.98                     | 3.28          |  |  |  |  |

| 3.2               | 3.19                     | 3.37          |  |  |  |  |

Table 13. 2.0 to 3.2 GHz Tuning Range Specification for  $AV_{DD}$  = 2.5 V (VCO Center Frequency is Approximate)

| VCO Setting (GHz) | AV <sub>DD</sub> = 2.5 V |               |  |  |  |  |

|-------------------|--------------------------|---------------|--|--|--|--|

|                   | VCO Min (GHz)            | VCO Max (GHz) |  |  |  |  |

| 2.0               | 1.96                     | 2.10          |  |  |  |  |

| 2.25              | 2.12                     | 2.30          |  |  |  |  |

| 2.5               | 2.37                     | 2.56          |  |  |  |  |

| 2.75              | 2.52                     | 2.70          |  |  |  |  |

| 3.0               | 2.87                     | 3.09          |  |  |  |  |

| 3.2               | 3.09                     | 3.28          |  |  |  |  |

#### **Frequency Acquisition**

A frequency detector (FD) circuit is employed to determine the frequency difference between the input data and the VCO frequency. Four registers are used to determine the frequency window detector (FWD) characteristics.

First, register WDET\_CTRL[4:1] determines the VCO pre-scale value, denoted as N, then register REF\_WIN[7:0] sets the reference frequency window, denoted as W<sub>ref.</sub> The out-of-lock window is set with register NRW\_WIN[7:0] (W<sub>narrow</sub>) and the in-lock window is set with register WIDE\_WIN[7:0] (W<sub>wide</sub>).

When output terminal LOL = H, the PLL is out-of-lock, and a narrow window is used to bring the VCO close to the locking frequency. When output terminal LOL = L, the PLL is in-lock and a wide window signals an out-of-lock condition.

#### Window Frequency Computation

The window frequency is computed as:

$$\begin{split} F_{narrow} &= \frac{W_{narrow}}{W_{ref}} \times 4 \times \frac{f_{vco}}{N} \ \text{(Used for terminal LOL= H to L)} \\ F_{wide} &= \frac{W_{wide}}{W_{ref}} \times 4 \times \frac{f_{vco}}{N} \ \text{(Used for terminal LOL= L to H)} \end{split}$$

The defaults are:

N = 1536 W<sub>narrow</sub> = 08h W<sub>wide</sub> = B4h W<sub>ref</sub> = 5

This implies a 4,167 ppm narrow window and a 93,750 ppm wide window. For OC-48, this translates into windows of 10.4 MHz and 234.4 MHz, respectively. Large values of the W registers will increase the frequency resolution and may also increase the window sample time, which will affect the acquisition time.

Table 14 contains recommended register settings that provide robust frequency acquisition performance for various bit rates. Note that the window values are different for each of the VCO divider ratios and the values listed are decimal values. These suggested values should be considered for use as initial settings, the optimum values for each application may vary slightly.

Table 14. Example Register Settings for Wide and Narrow Frequency Windows (values are in decimal format)

| For VCO Divider Ratio:                                            | 1    | 2    | 4    | 8    | 16   | 32    |

|-------------------------------------------------------------------|------|------|------|------|------|-------|

| Ref window address 00h, 40h, 80h, C0h                             | 20   | 40   | 80   | 80   | 80   | 80    |

| Narrow window address 01h, 41h, 81h, C1h                          | 58   | 58   | 58   | 58   | 58   | 58    |

| Wide window address 02h, 42h, 82h, C2h                            | 59   | 59   | 59   | 59   | 59   | 59    |

| Window detector divide ratio address 03h, 43h, 83h, C3h, bits 4:1 | 1536 | 1536 | 1536 | 3072 | 6144 | 12288 |

With the signal LOLinternal = 1, the frequency acquisition loop (FAL) is enabled to drive the VCO to the narrow frequency window. When the VCO is within the window, the CDR loop is left to obtain phase lock. With signal LOLinternal = 0, the FAL is not enabled until the VCO frequency is beyond the wide window. The signal LOL internal that controls the FAL can be enabled only with a loss of lock (register WDET\_CTRL[0] = 0, default), or either the loss of lock or loss of signal (register WDET\_CTRL[0] = 1).

The LOL hysteresis function (register WDET\_CTRL[7:6] Lol\_hyst, address 03h) programs the number of consecutive identical internal loss of lock decisions that must occur before the loss of lock status is modified. This function is controlled by bits 6 and 7 of register 03h, and the default value is to update loss of lock status after one decision.

#### Data Phase Lock

When the VCO frequency is within the frequency window, the CDR PLL must acquire and maintain phase lock in relationship to the input data. A linear self-centering phase detector centers the clock within the data. SmartCenter<sup>TM</sup> circuitry in the phase detector (PD) circuit stabilizes the sampling point for process, temperature, power supply, and transition density. With real data, the pattern transition density can change, especially in the A1/A2 bytes in a SONET header. This can cause pattern- dependent jitter if the related PD phase-transfer curves do not intersect at the static phase operating point.

The primary feature of SmartCenter<sup>™</sup> is to minimize this source of jitter. The secondary SmartCenter<sup>™</sup> feature ensures the clock/ data phase-lock relationship is centered within the phase-margin of the decision flip-flop, and provide maximum jitter tolerance over the SONET specifications.

SmartCenter<sup>TM</sup> can be disabled with register MAST\_CTRL[0] = 0 and powered off with register MAST\_CTRL[1] = 1. The SmartCenter<sup>TM</sup> default is power on and enabled.

#### Loop Filter

A differential RC loop filter is used for low noise and low jitter operation. The CX20501 includes an integrated resistor and capacitor with programmable values so that the loop filter frequency response can be modified for different data rates. In addition to the integrated loop filter components, some external components are required to implement the complete loop filter. See Figure 5 for an illustration of the loop filter topology showing the integrated components as well as recommended external components. The phase detector charge-pump connects between LPPp and LPPn and the frequency detector charge pump connects between LPPf and LPPn. The recommended external loop filter component configuration is shown in Figure 6. A series capacitor with a value of 100 nF should be placed between LPPf and LPPn, and a shunt capacitor with a value of 20 pF should be placed between LPPp and LPPn. If the programmable loop-filter is not desired, connect an external 150 $\Omega$  low-noise series resistor between LPPp and LPPf in addition to the recommended external series and shunt capacitors.

By default, the data rate selected through VCO\_DIV[2:0] programs the correct values for the integrated loop filter components for different SONET rates. LOOP\_FILTER[7] = 1 will bypass this default auto-selection, and LOOP\_FILTER[6:3] (damping) and LOOP\_FILTER[2:0] (bandwidth) set the effective RC value. With auto-selection disabled, the default condition is LOOP\_FILTER[6:3] = 0111b and LOOP\_FILTER[2:0] = 000b, the latter disabling (open) the internal resistor. If an internal resistor is not selected by LOOP\_FILTER[2:0] = 000b, an external resistor of 150 ohms is needed in addition to the two external capacitors. Table 15 summarizes the manual settings, which are used with non-SONET bit rates. In either the auto or manual loop mode, LOOP\_TRIM[2:0] provides a trim register for 60% to 130% trim (default is 60% (000b), 100% (100b) should be set for OC-48 operation). This can be used to optimize the performance, especially for nonstandard bit rates.

See Table 15 when selecting internal capacitor and resistor settings.

Figure 5. Internal RC Loop Filter Fine Tune with Recommended External Capacitors

### Figure 6. External Loop Filter Configuration

### Table 15. Loop Filter Selection

| Data Rate (Gbps) | Max. Bandwidth (MHz) | Peaking (dB) | Resistor (Ω) <sup>(1)</sup> | Damping value <sup>(1)</sup> |

|------------------|----------------------|--------------|-----------------------------|------------------------------|

| 3.1250           | 2.3                  | <0.06        | 150                         | 340                          |

| 2.7000           | 2.0                  | <0.06        | 150                         | 320                          |

| 2.4880           | 1.9                  | <0.06        | 150                         | 300                          |

| 2.0000           | 1.5                  | <0.06        | 150                         | 240                          |

| 1.2500           | 0.95                 | <0.06        | 300                         | 150                          |

| 1.0625           | 0.75                 | <0.06        | 300                         | 120                          |

| 0.622            | 0.45                 | <0.06        | 600                         | 75                           |

| 0.311            | 0.23                 | <0.06        | 1200                        | 36                           |

| 0.155            | 0.10                 | <0.06        | 2400                        | 18                           |

| 0.77             | 0.055                | <0.06        | 4800                        | 9                            |

### Loss-Of-Signal

The input data is compared to a threshold in the LOS detector to determine if a signal is present at the input of the CDR or not. There is hysteresis designed into the LOS detector such that the threshold levels are different for a L-H transition and for a H-L transition. The thresholds are set such that LOS will be asserted high if the p-p amplitude of the input signal is below approximately 56 mV.

Once LOS is asserted, the signal will be held high until the p-p input amplitude is greater than approximately 240 mV. If the p-p amplitude of the input signal is greater than 240 mV, then LOS will be held low. If the p-p amplitude of the input signal is between 56 mV and 240 mV, the status of LOS is undefined, and could be high, low, or toggling.

Since the LOS detector looks at the average threshold crossing, the LOS detector has an associated bandwidth. When LOS = L, the default bandwidth of 7.9 KHz (set by LOS\_CTRL[7:6]) minimizes false LOS L-to-H transitions with the CDR in-lock.

To quickly enable LOS H-to-L transitions, the LOS = H default bandwidth is 800 KHz (set by LOS\_CTRL[5:4]).

#### Loss-Of-Signal and Loss-Of-Lock Bussing

For applications with one or more CX20501 devices, both the *LOL* and *LOS* can be wired "OR". In this case, the outputs of *LOS* or *LOL* will be at a logic high when a loss alarm is active. When the alarm is not active, the outputs will be in a high impedance state instead of logic low. Without any alarms, all outputs are three-stated and requires an external 100 K $\Omega$  pull-down resistor connected to *DVss*. This feature is enabled for Loss-Of-Signal with *OUTBF\_CTRL*[5] = 1 (default) and for Loss-Of-Lock with *OUTBF\_CTRL*[4] = 1 (default). When either bit is set to 0 and the alarm is not active, the output is pulled low to maintain backward compatibility with the CX20464. When the alarm is enabled, the alarm status of the four CDRs can be read from *LOX\_STAT1*[7:0] & *LOX\_STAT2*[7:0].

| LOX_STAT1/2[7] is LOS for CDR#3 | LOX_STAT1/2[3] is <b>LOS</b> for CDR#1 |

|---------------------------------|----------------------------------------|

| LOX_STAT1/2[6] is LOL for CDR#3 | LOX_STAT1/2[2] is LOL for CDR#1        |

| LOX_STAT1/2[5] is LOS for CDR#2 | LOX_STAT1/2[1] is LOS for CDR#0        |

| LOX_STAT1/2[4] is LOL for CDR#2 | LOX_STAT1/2[0] is <b>LOL</b> for CDR#0 |

When the Loss-Of-Signal circuit is powered down, it is forced low when the buss mode is not selected and forced to a high-Z state when the buss mode is selected. LOX\_STAT1[7:0] always reflects the current status of the alarms. When any individual alarm changes from a no-alarm to an alarm condition, the alarm bit can be immediately read from LOX\_STAT2[7:0]. The alarm bit stays in the alarm condition until LOX\_STAT2[7:0] is read, after which the contents of LOX\_STAT1[7:0] are copied to LOX\_STAT2[7:0]. If the alarm condition has been resolved, it will clear upon read; if the alarm condition persists, it will remain in an alarm state. A value of '1' in an alarm register indicates the alarm is high (asserted), a value of '0' indicates the alarm is low (not-asserted).

If the *LOS/LOL* bussing function is not enabled ( $OUTBF\_CTRL[5/4] = 0$ ), the *LOS* and *LOL* pins and *LOX\_STAT1*[7:0] reflect the current status. If the *LOS/LOL* bussing function is enabled ( $OUTBF\_CTRL[5/4] = 1$ ),  $LOX\_STAT1$ [7:0] always reflects the current status of *LOS* and *LOL*. When bussed, *MAST\\_CTRL2*[3] = 0 (default) leaves the *LOS* and *LOL* output pins in a high-Z state. When not bussed, *MAST\\_CTRL2*[3] = 1 sets the *LOS* and *LOL* output pins to reflect the current actual status.

### **Clock to Data Output Timing**

The clock and data output skew timing is defined in Figure 7.

### Figure 7. Clock and Data Output Skew Timing

The specifications for the clock and data output skew are shown in Table 16, and the specifications for the clock output duty cycle are shown in Table 17.

#### Table 16. Clock to Data Output Skew

| Symbol          | ltem                                | Min. | Тур. | Max. | Units |

|-----------------|-------------------------------------|------|------|------|-------|

| Т <sub>SK</sub> | Skew relative to clock falling edge | 245  | 320  | 390  | ps    |

### Table 17. Clock and Data Output Duty Cycle

| Symbol          | Item                    | Min. | Тур. | Max. | Units |

|-----------------|-------------------------|------|------|------|-------|

| C <sub>DC</sub> | Clock output duty cycle | 47   | 49.4 | 52.5 | %     |

| D <sub>DC</sub> | Data output duty cycle  | 44.5 | 49.4 | 54.5 | %     |

#### **CDR Bypass**

In cases where the input data exceeds the operating range of the CX20501, the CDR re-timing function can be bypassed with *MAST\_CTRL2*[4] = 1 (default is with re-timing). Loss-Of-Signal and the Loss-Of-Lock continue to function.

#### Resetting the CDR

Three different resets are available on the CX20501, one hardware reset and two types of software resets. Any of the three resets loads the default values into the CDR registers of the device. A hardware reset is required after initial power up and is executed by holding the xRST pin low for a minimum of 20 ns, then pulling the xRST pin high. The CX20501 will be available within 20 ns after the xRST pin returns to a high state. In addition to the hardware reset, there are two software resets: A global software reset which resets all four CDRs and an individual software reset that resets a specific CDR channel while leaving the other three CDR channels undisturbed. The global reset is register address 21h and the individual software reset registers are addresses 11h, 51h, 91h, and D1h. To issue either type of software reset, two consecutive writes of AAh to the appropriate address is required. The first write of AAh

puts the device/channel into reset and the second brings the device/channel out of reset.

#### Output Drive Level

$OUTBF\_CTRL[3:2]$  controls the clock drive level and powers the buffer on/off. By default, the register selects power-on, low swing. All four clock outputs are controlled by the **xENCLK** pin. If **xENCLK** = H, all outputs are off (hardware clock disable has priority over register settings for 500 mV output swing). If **xENCLK** = L, the software register, which defaults to low swing for the clock outputs, controls the output drivers.  $OUTBF\_CTRL[1:0]$  selects the output drive level and power the data output driver on/off. The default value is data buffer power-on with low swing.

To minimize noise propagation when several CDRs are chained together, as in a cross-connect application, an inhibit mode is controlled by MAST\_CTRL2[6:5].

*MAST\_CTRL2*[6:5] = 00b (default) disables the inhibit

01b is a software forced inhibit

10b is inhibit with *LOL* = H only

11b is inhibit with *LOL* or *LOS* = H.

When the inhibit feature is enabled, the output is held H if  $MAST\_CTRL2[7] = 1$  (default), or L if  $MAST\_CTRL2[7] = 0$ . This feature is automatically disabled if the CDR bypass is enabled. If the output is powered down, the inhibit feature will have no effect until the output driver is powered up. When powered down, the output driver bias is shut-off and both the positive and negative outputs have a 50  $\Omega$  pull-up.

#### **Other Features**

The *MAST\_CTRL*[2] = 1-bit will power-down individual CDR blocks to save power. By default, all four CDRs will power-on after a reset.

**NOTE:** The serial interface is always on. To minimize noise, SLOPE\_CTRL can control the internal / external CMOS bus / serial interface edge rate. For low-speed operation, a slower edge rate reduces the potential of noise generated by the CMOS data edges. For higher speed interface, the edge rate can be increased. This register is global to all CDRs.

For telecom applications, the CHIP\_REV register contains the current CX20501 revision. This register is global to all CDRs. The PART\_NUMBER register contains an ID code for this part. Please refer to the latest product bulletin for details on the CHIP\_REV register contents for the CX20501.

#### Serial Interface

The CDR functions of the CX20501 are controlled by an 8-bit register. The 8-bit register address and 8-bit data contents are addressed with a serial I/O interface. The different addresses of each register are mapped to a specific function so data can be read from or written to the registers.

#### Serial I/O Overview

The serial I/O operation is gated by chip select signal xCS (on input terminal xCS). Data is shifted in on terminal SDI on the falling edge of the serial I/O clock input (terminal SCIk), and shifted out on the serial data output (terminal SDO) on the rising edge of SCIk. To address a register, a 10-bit input consists of the first bit (start bit, SB = 1), the second bit (operation bit: OP = 1 for read, OP = 0 for write), followed by the 8-bit address (most significant bit [MSB] first).

#### Timing Diagram: Clock Set and Program Modes

The timing diagrams for the serial write and read operations are shown in Figure 8 and Figure 9, respectively. Table 18 contains the specifications for the various timing parameters for the serial programming interface.

To initiate a write sequence, as shown in Figure 8, xCS goes low before the falling edge of SCLK. On each falling edge of SCLK, the 18-bits consisting of the SB = 1, OP = 0, ADDR, and DATA, are latched into the input shift register. The rising edge of xCS must occur before the falling edge of SCLK for the last bit. Upon receipt of the last bit, one additional cycle of SCLK is necessary before the input DATA transfers from the input shift register to the addressed register. If consecutive read/write cycles are being performed, it is not necessary to insert an extra clock cycle between read/write cycles, however one extra clock cycle is needed after the last data bit of the final read/write cycle to complete the operation.

On a Write cycle, any bits that follow the expected number of bits are ignored, and only the first 16-bits following SB and OP are used.

Figure 9 illustrates the serial Read mode timing diagram. To initiate a read sequence, xCS goes low before the falling edge of SCLK. On each falling edge of SCLK, the 10-bits consisting of SB = 1, OP = 1, and the 8-bit ADDR are written to the serial input shift register of the CX20501. On the first rising edge following the address LSB, the SB and 8-bits of the DATA are shifted out on SDO. The first bit output on SDO for a read operation is always 0.

On a Read cycle, any extra clock cycles will result in the repeat of the data LSB. An invalid SB or OP renders the operation undefined. The falling edge of xCS always resets the serial operation for a new Read or Write cycle. Table 18 contains the timing specifications for the serial programming interface.

#### Figure 8. Serial Write Mode

| Symbol                      | Item                      | Notes | Minimum | Typical | Maximum  | Units |

|-----------------------------|---------------------------|-------|---------|---------|----------|-------|

| t <sub>dw</sub>             | Data width                | _     | 20      | _       | _        | ns    |

| t <sub>dh</sub>             | Data hold time            | _     | 13      |         | _        | ns    |

| t <sub>ds</sub>             | Data setup time           | _     | 4.4     | -       | _        | ns    |

| t <sub>ens</sub>            | Enable setup time         | _     | 3.7     | _       | _        | ns    |

| t <sub>cs</sub>             | Chip select setup time    | _     | 3       | _       | Tclk – 3 | ns    |

| t <sub>ch</sub>             | Chip select hold time     | _     | 3.6     | -       | _        | ns    |

| t <sub>rdd</sub>            | Read data output delay    | _     | 8.6     | _       | 23       | ns    |

| t <sub>rds</sub>            | Read data valid           | _     | 11      | _       | _        | ns    |

| t <sub>clk</sub>            | SCLK period width         | _     | 20      | _       | _        | ns    |

| t <sub>wclk</sub>           | SCLK minimum low duration | _     | 5       |         | Tclk – 5 | ns    |

| t <sub>r</sub>              | Output rise time          | 1     | —       | _       | 0.66     | ns    |

| t <sub>f</sub>              | Output fall time          | 1     | —       | —       | 0.54     | ns    |

| Note:<br>1. Edge rate in th | ne high edge-rate mode.   | I     | 1       |         | 1        |       |

Table 18. Serial Interface Timing—Specified at Recommended Operating Conditions

### Table 19. Register Summary

| Address | Name        | d7          | d6          | d5         | d4         | d3        | d2         | d1         | d0         |

|---------|-------------|-------------|-------------|------------|------------|-----------|------------|------------|------------|

| 00h     | REF_WIN     | RefWin[7]   | RefWin[6]   | RefWin[5]  | RefWin[4]  | RefWin[3] | RefWin[2]  | RefWin[2]  | RefWin[0]  |

| 01h     | NRW_WIN     | NrwWin[7]   | NrwWin[6]   | NrwWin[5]  | NrwWin[4]  | NrwWin[3] | NrwWin[2]  | NrwWin[2]  | NrwWin[0]  |

| 02h     | WIDE_WIN    | WdWin[7]    | WdWin[6]    | WdWin[5]   | WdWin[4]   | WdWin[3]  | WdWin[2]   | WdWin[2]   | WdWin[0]   |

| 03h     | WDET_CTRL   | Lol_hyst[7] | Lol_hyst[6] | "0"        | VcoDiv[3]  | VcoDiv[2] | VcoDiv[1]  | VcoDiv[0]  | FacqMod    |

| 04h     | OUTBF_CTRL  |             |             | LOSmode    | LOLmode    | ClkLvl[1] | ClkLvl[0]  | DataLvl[1] | DataLvl[0] |

| 05h     | LOS_CTRL    | LosBiL[1]   | LosBiL[0]   | LosBoL[1]  | LosBoL[0]  | "0"       | "0"        | "1"        | "0"        |

| 06h     | MAST_CTRL   |             |             | "1"        | "1"        | "1"       | PdAll      | PdSmCtr    | EnSmCtr    |

| 07h     | VCO_CTRL    | "0"         | VcoFreq[2]  | VcoFreq[1] | VcoFreq[0] |           | "1"        | "0"        | "0"        |

| 09h     | PD_CTRL0    | PdDCservo   | "0"         | "0"        | PdLOS      | "0"       | "0"        | "0"        | "0"        |

| 0Eh     | VCO_DIV     |             |             |            |            |           | Freqdiv[2] | Freqdiv[1] | Freqdiv[0] |

| 0Fh     | LOOP_FILTER | Force       | Damp[3]     | Damp[2]    | Damp[1]    | Damp[0]   | Bw[2]      | Bw[1]      | Bw[0]      |

| 10h     | LOOP_TRIM   |             |             |            |            |           | Trim[2]    | Trim[1]    | Trim[0]    |

| 11h     | ISOFT_RES   | "1"         | "0"         | "1"        | "0"        | "1"       | "0"        | "1"        | "0"        |

| 12h     | MAST_CTRL2  | InhPol      | Inhibit[1]  | Inhibit[0] | Bypass     | ByPFForce |            |            |            |

| ()      |             |             |             |            |            |           |            |            |            |

| 20h     | SLOPE_CTRL  |             |             | Int[1]     | Int[0]     |           |            | Ext[1]     | Ext[0]     |

| 21h     | GSOFT_RES   | "1"         | "0"         | "1"        | "0"        | "1"       | "0"        | "1"        | "0"        |

| 22h     | CHIP_REV    | rev[7]      | rev[6]      | rev[5]     | rev[4]     | rev[3]    | rev[2]     | rev[1]     | rev[0]     |

| 23h     | PART_NUM    | "0"         | "0"         | "0"        | "0"        | "0"       | "0"        | "1"        | "0"        |

| 26h     | LOX_STAT1   | LOS3        | LOL3        | LOS2       | LOL2       | LOS1      | LOL1       | LOS0       | LOL0       |

| 27h     | LOX_STAT2   | LOS3        | LOL3        | LOS2       | LOL2       | LOS1      | LOL1       | LOS0       | LOL0       |

| ()      |             |             |             |            |            |           |            |            |            |

| 40h     | Repeat CDR1 |             |             |            |            |           |            |            |            |

| 80h     | Repeat CDR2 |             |             |            |            |           | <u> </u>   |            |            |

| C0h     | Repeat CDR3 |             |             |            |            |           |            |            |            |

1. Undefined addresses and bits are reserved for Mindspeed's use only. A 0 should be written to all undefined bits.

2. Block 20h to 25h is common to all four CDRs.

### Table 20. Register Description (Sheet 1 of 7)

| 00h, 40h, 80h, C0h: Reference Window |              |                                                                                                                                        |  |  |

|--------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REF_WIN                              | [7:0] RefWin | Defines reference window (VCO count period) for the frequency detection timing period.<br>Default RefWin[7:0] = 05h = W <sub>ref</sub> |  |  |

| 01h, 41h, 81h, C1h: Narrow Window |              |                                                                                                                  |  |  |

|-----------------------------------|--------------|------------------------------------------------------------------------------------------------------------------|--|--|

| NRW_WIN                           | [7:0] NrwWin | Defines narrow frequency window used to signal LOLinternal = 1 to 0.<br>Default NrwWin[7:0] = $08h = w_{narrow}$ |  |  |

| 02h, 42h, 82h, C2h: Wide Window |             |                                                                                                                          |  |  |

|---------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| WIDE_WIN                        | [7:0] WdWin | Defines wide frequency window used to signal LOLinternal = 0 to 1.<br>Default WdWin[7:0] = B4h = 180d= w <sub>wide</sub> |  |  |

### Table 20. Register Description (Sheet 2 of 7)

| 03h, 43h, 83h, C3l | h: Window Detector Contro | bl                                        |                                                                                                                                                                                                                                                                                                   |                                                                                                                |  |  |

|--------------------|---------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| WDET_CTRL          | [7:6] Lol_hyst            | 00 = LOL ge<br>01 = LOL ge<br>10 = LOL ge | Defines hysteresis for LOL detection:<br>00 = LOL gets updated after first detection (default)<br>01 = LOL gets updated after two consecutive equal LOL values<br>10 = LOL gets updated after three consecutive equal LOL values<br>11 = LOL gets updated after four consecutive equal LOL values |                                                                                                                |  |  |

|                    | [5] MSPD reserved         | Mindspeed r                               | eserved bit, set                                                                                                                                                                                                                                                                                  | to 0.                                                                                                          |  |  |

|                    | [4:1] VcoDiv              |                                           |                                                                                                                                                                                                                                                                                                   | ider ratio (N) for Window Detector<br><sub>(wide   narrow)</sub> / w <sub>ref</sub> * 4 * f <sub>vco</sub> / N |  |  |

|                    |                           | VcoDiv                                    | N                                                                                                                                                                                                                                                                                                 | Bandwidth                                                                                                      |  |  |

|                    |                           |                                           |                                                                                                                                                                                                                                                                                                   | $(f_{vco} = 2.5 \text{ GHz}, w_{(wide   narrow)} = w_{ref})$                                                   |  |  |

|                    |                           | 0000:                                     | 256                                                                                                                                                                                                                                                                                               | 39.1 MHz                                                                                                       |  |  |

|                    |                           | 0001:                                     | 512                                                                                                                                                                                                                                                                                               | 19.5 MHz                                                                                                       |  |  |

|                    |                           | 0010:                                     | 768                                                                                                                                                                                                                                                                                               | 13.0 MHz                                                                                                       |  |  |

|                    |                           | 0011:                                     | 1024                                                                                                                                                                                                                                                                                              | 9.8 MHz                                                                                                        |  |  |

|                    |                           | 0100:                                     | 1536 (default)                                                                                                                                                                                                                                                                                    | 6.5 MHz                                                                                                        |  |  |

|                    |                           | 0101:                                     | 2048                                                                                                                                                                                                                                                                                              | 4.9 MHz                                                                                                        |  |  |

|                    |                           | 0110:                                     | 3072                                                                                                                                                                                                                                                                                              | 3.255 MHz                                                                                                      |  |  |

|                    |                           | 0111:                                     | 4096                                                                                                                                                                                                                                                                                              | 2.441 MHz                                                                                                      |  |  |

|                    |                           | 1000:                                     | 6144                                                                                                                                                                                                                                                                                              | 1.628 MHz                                                                                                      |  |  |